ホーム >

システム ビジョン デザイン > 64×64 画素を搭載したプログラマブルなビジョンチップ

64×64 画素を搭載したプログラマブルなビジョンチップ

概要

近年,半導体集積化技術の進歩や,画像処理を手軽に扱いたいというニーズの高まりから,画像処理を専門に扱うプロセッサをワンチップ化する動きが進んでいる.

しかし,従来の画像処理用プロセッサは,その並列性により主に初期視覚処理に対して強い威力を発揮するが,より高度な処理を行おうとした場合に,非局所演算が不得手であることや,画素数と汎用性の間にトレードオフが存在することなどの問題があった.

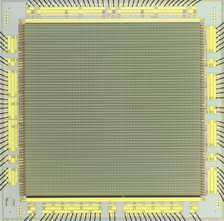

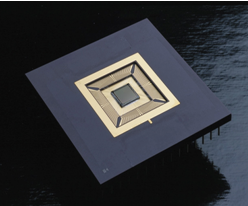

そこで,イメージセンサの画素ごとにPEを取り付けることで,高フレームレートの画像処理を実現するビジョンチップの開発を行った.開発したビジョンチップは,64×64 画素を搭載し,プログラマブルで処理を与えることが可能である.演算回路には新たに設計した動的再構成可能なSIMDアーキテクチャを採用している.0.35μm CMOS プロセスを使用しており,チップサイズは5.4mm×5.4mm である.各画素の面積は 67.4μm×67.4μm であり,256×256画素が 約 1.8cm 角のチップに乗る計算である.

参考文献

- 小室孝, 鏡慎吾, 石川正俊:ビジョンチップのための動的再構成可能なSIMDプロセッサ, 電子情報通信学会論文誌 D-II, Vol.J86-D-II, No.11, pp.1575-1585 (2003) [PDF]