Home >

System Vision Design >

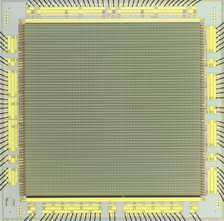

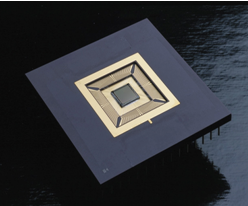

A Programmable Vision Chip with 64x64 pixels

A Programmable Vision Chip with 64x64 pixels

Summary

A programmable vision chip that integrates 64x64 pixels has been developed. It adopts newly designed dynamically reconfigurable SIMD architecture for processing circuits. It is fabricated using 0.35um CMOS process and the chip size is 5.4mm x 5.4mm. Each pixel area is 67.4um x 67.4um and 256x256 pixels could be integrated on about 1.8cm square chip.

Reference

- Takashi Komuro, Shingo Kagami, Masatoshi Ishikawa: A Dynamically Reconfigurable SIMD Processor for a Vision Chip, IEEE Journal of Solid-State Circuits, Vol. 39, No. 1, pp. 265-268 (2004) [PDF]