ホーム >

システム ビジョン デザイン > 動的再構成可能なSIMD型超並列処理アーキテクチャ

動的再構成可能なSIMD型超並列処理アーキテクチャ

概要

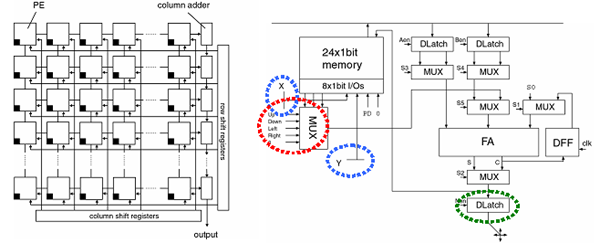

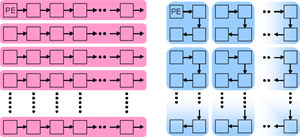

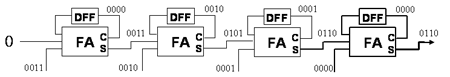

PE 同士を結合させる機能を持たせ、ハードウェアを動的に再構成可能にした、 ビジョンチップのための新しい SIMD プロセッサのアーキテクチャを設計した。 このアーキテクチャでは、ビジョンチップにおける画素数と汎用性の間のトレードオフを解決している上、 従来の超並列 SIMD プロセッサが苦手とした非局所演算を効率的に実行できるという特徴を持つ。

Fig.1 アーキテクチャ

Fig.2 PE 同士の結合

Fig.3 結合 PE の演算例(累積加算)

参考文献

- 小室孝, 鏡慎吾, 石川正俊:ビジョンチップのための動的再構成可能なSIMDプロセッサ, 電子情報通信学会論文誌D-II, Vol.J86-D-II, No.11, pp.1575-1585 (2003) [PDF]