ホーム >

システム ビジョン デザイン > ソニーと東京大学石川渡辺研究室が共同で開発したビジョンチップ

ソニーと東京大学石川渡辺研究室が共同で開発したビジョンチップ

概要

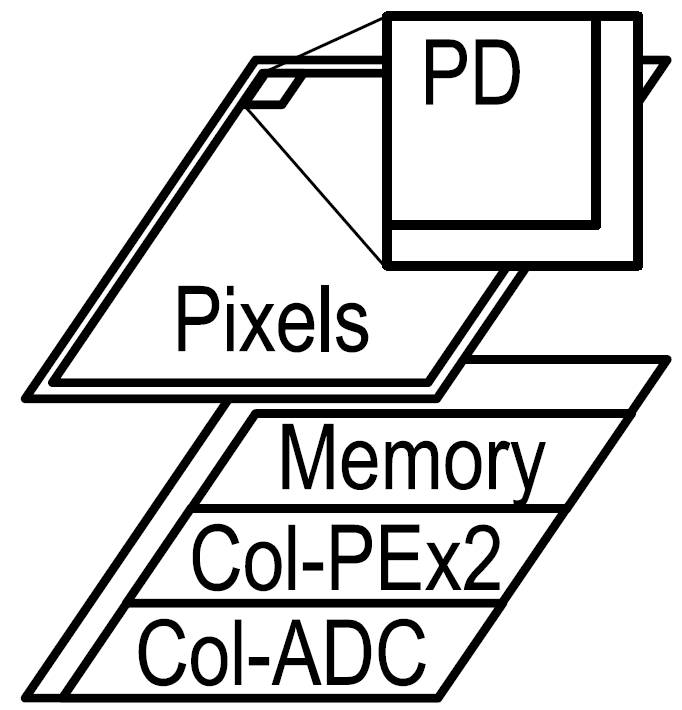

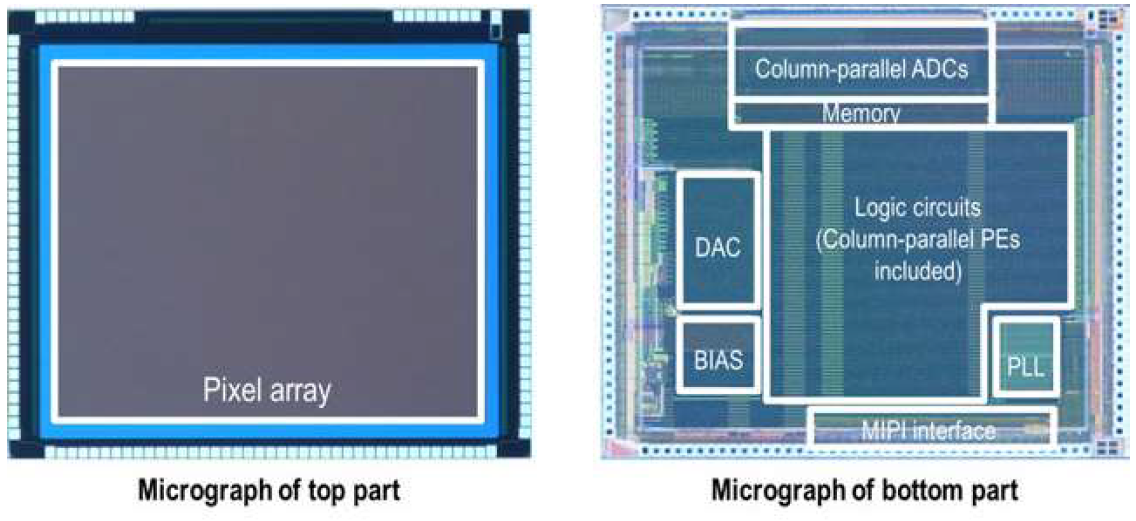

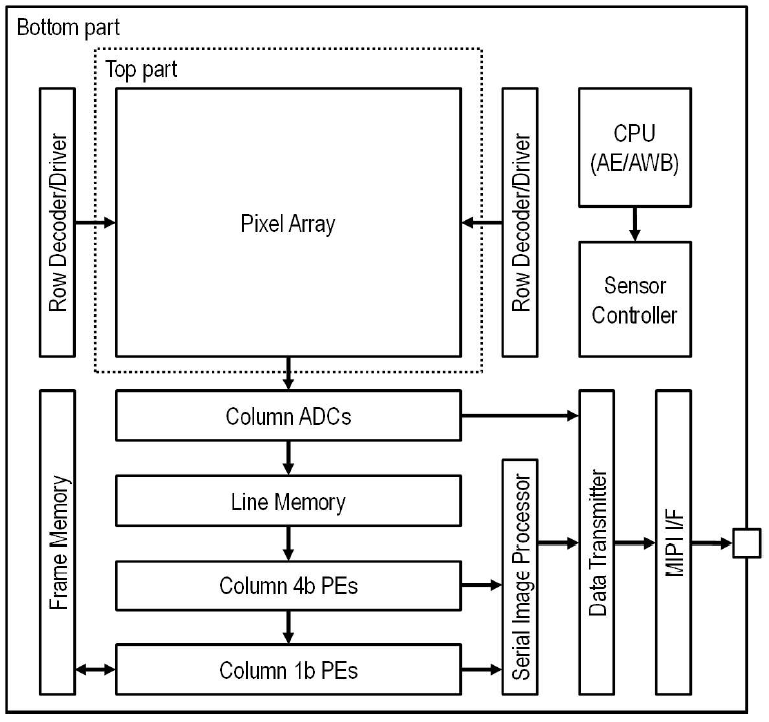

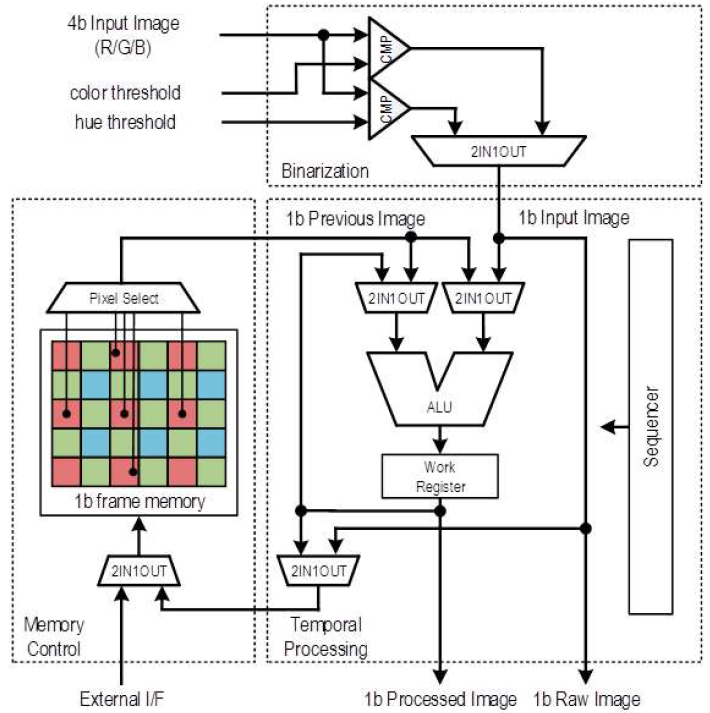

高速かつ頑健なビジョンシステムへの応用に向けて, ソニーと東京大学石川渡辺研究室が共同でビジョンチップを開発した. 開発したビジョンチップはPEやメモリ等の周辺回路をイメージセンサに積層することで, PD,PE双方の面積を確保し,高い撮像性能と高い処理性能を両立している. PD部は90nmのプロセスで製作されており,1/3.2インチ型,1.27Mピクセル, 裏面照射型の高感度イメージャが採用されている. また,PE部は40nmのプロセスで製作されており,1ミリ秒での画像処理に対応した 列並列PE,列並列ADC,フレームメモリ等が搭載されている. PE部では色やヒストグラムを用いた空間的なフィルタリングに加えて, フレームメモリを利用した時間的なフィルタリング機能を備えており, モーメントや運動方向の計算など,対象の撮像から検出,認識,追跡といった様々な処理を ワンチップで実現することが可能である. これらの画像処理機能をチップ上で実現することにより, 1000fpsという高速動作時も消費電力は最大363mWに抑えられており, センサーと計算機を別にした従来システムに対し,高速性と頑健性を維持, または向上させつつ,省スペース化や省電力化が可能であると考えられる.

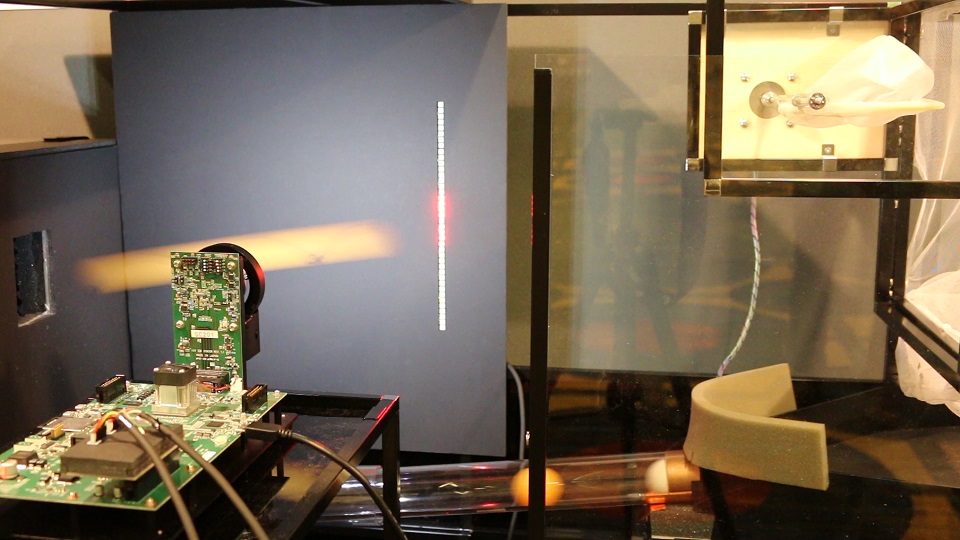

2017年2月に開催された半導体回路の国際会議ISSCC 2017では, 本チップの140GOPSの処理が可能な列並列PEを利用し, 時空間フィルタリングをプログラムすることで, 高速に運動するボールを1msで認識し、その色に応じて捕球するデモが行われた. 本デモンストレーションのように,ビジョンチップを利用することで, 高速,低遅延,小型,低電力の様々な応用の実現が期待される.

Fig. 1: ビジョンチップのアーキテクチャ模式図と顕微鏡写真*1.

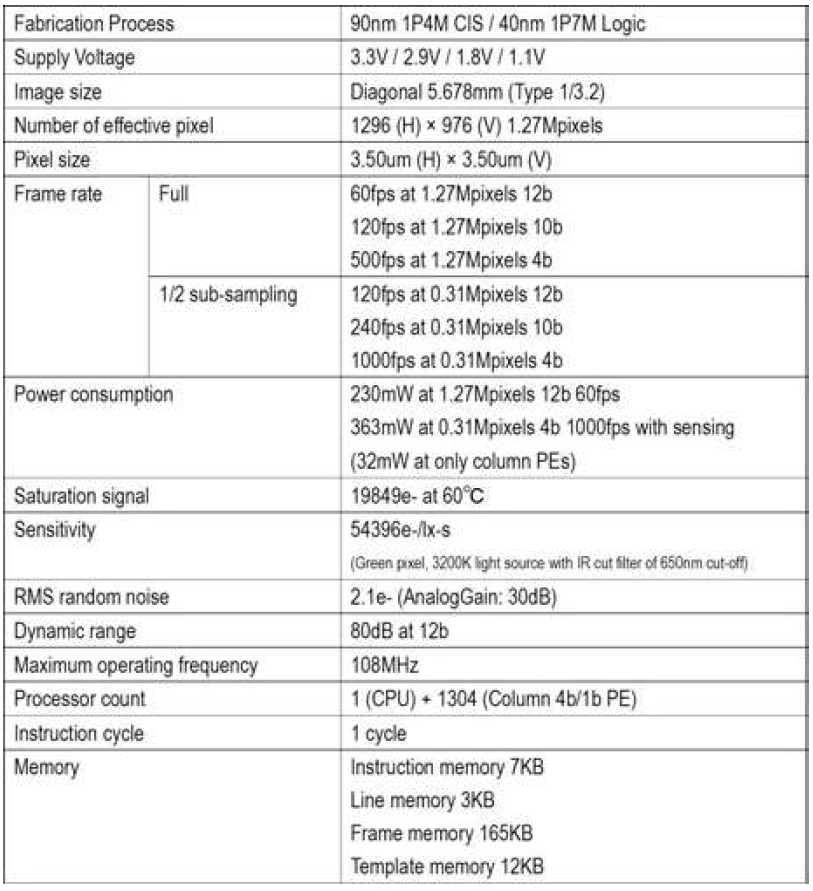

Fig. 2: ブロックダイアグラムと仕様表*1.

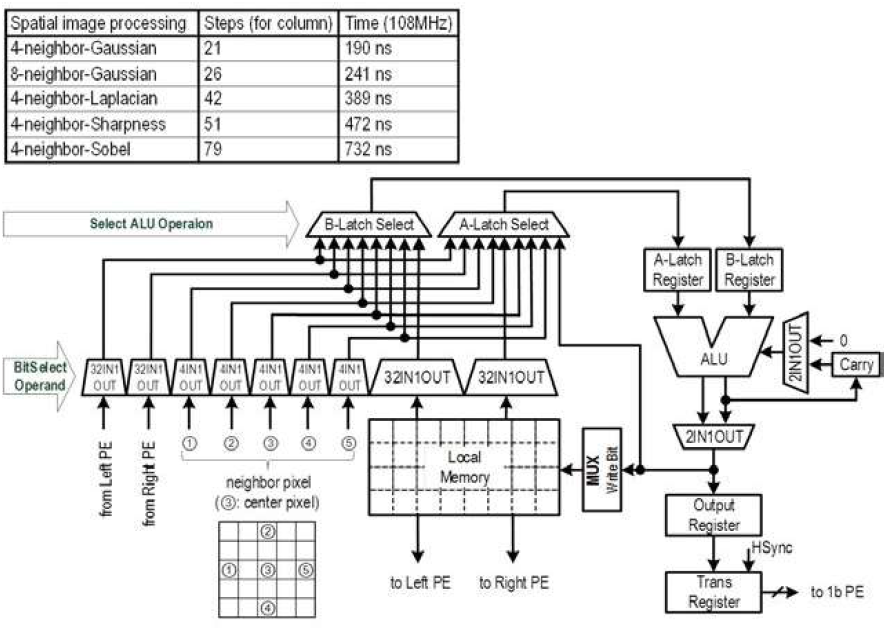

Fig. 3: PEにおける処理のブロック図*1.

*1 図は下記論文の図より引用.

T. Yamazaki, H. Katayama, S. Uehara, A. Nose, M. Kobayashi, S. Shida, M. Odahara, K. Takamiya, Y. Hisamatsu, S. Matsumoto, L. Miyashita, Y. Watanabe, T. Izawa, Y. Muramatsu, M. Ishikawa : A 1ms High-Speed Vision Chip with 3D-Stacked 140GOPS Column-Parallel PEs for Spatio-Temporal Image Processing, International Solid-State Circuits Conference (ISSCC 2017), Proceedings, pp.82-83, San Francisco, California, USA, 5-9 Feb. (2017)

Fig. 4: ISSCC2017で実演を行ったシステム

動画

動画の原本もございます.使用許諾は,contactまでご連絡下さい.

参考文献

- 小林正嗣, 山崎智裕, 片山博誠, 上原修二, 能勢敦, 志田さやか, 小田原正起, 高宮健一, 久松康秋, 松本静徳, 宮下令央, 渡辺義浩, 伊澤崇, 村松良徳, 石川正俊: 時空間処理のための140GOPS列並列演算器を有する積層型1ms-高速ビジョンチップ, 映像情報メディア学会情報センシング研究会 (東京, 2017.3.10)/映像情報メディア学会技術報告, Vol.41, No.10, pp.3-6.

- T. Yamazaki, H. Katayama, S. Uehara, A. Nose, M. Kobayashi, S. Shida, M. Odahara, K. Takamiya, Y. Hisamatsu, S. Matsumoto, L. Miyashita, Y. Watanabe, T. Izawa, Y. Muramatsu, M. Ishikawa : A 1ms High-Speed Vision Chip with 3D-Stacked 140GOPS Column-Parallel PEs for Spatio-Temporal Image Processing, International Solid-State Circuits Conference (ISSCC 2017), Proceedings, pp.82-83, San Francisco, California, USA, 5-9 Feb. (2017)