ホーム >

システム ビジョン デザイン > ダイナミック回路を用いた320×240画素試作チップ

ダイナミック回路を用いた320×240画素試作チップ

概要

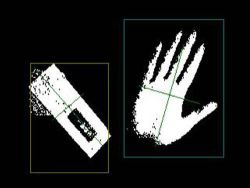

近年,工業製品検査や乗り物の緊急回避など,システム自動化の分野において,視覚情報が重要な役割を果たすようになってきた.これらのアプリケーションの実現には,画像から対象を抽出し,識別や姿勢推定を行う必要がある.このような処理は,画像の部分領域における画素値の重み付け総和である,画像モーメントを計算することで実現できる.

モーメント演算を高速に実行するためには強力なプロセッサが要求されるが,一般的に大型で高コストとなる問題がある.民生品や汎用組立ロボットなど,今後の需要拡大が期待される分野のニーズに応えるには,撮像と演算を1チップ化し,小型化・低コスト化を図る必要がある.また,多数の対象の抽出や不変量を利用した識別などを実現するには,高い解像度と高次モーメントの演算能力が必要である.

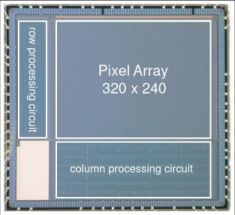

これらの要求を満たすため,我々はモーメント抽出に特化したCMOSスマートイメージセンサの開発を行った.ダイナミック回路を用いて画素回路の素子数を削減し、チップサイズ9.22mm×8.52mmに320×240画素を実装した.これはデジタルで演算を行うビジョンチップでは最大規模の画素数である.

参考文献

- Takashi Komuro, Atsushi Iwashita, Masatoshi Ishikawa: A QVGA-size Pixel-parallel Image Processor for 1,000-fps Vision, IEEE Micro, vol. 29 no. 6, pp. 58-67 (2009)

- 岩下貴司,小室孝,石川正俊: ダイナミック回路を用いた320×240画素ビジョンチップ, 映像情報メディア学会 情報センシング研究会(東京,2008.12.16)/映像情報メディア学会技術研究報告, Vol.32,No.57,(IST2008-84) pp.21-24 [PDF]