Home >

System Vision Design >

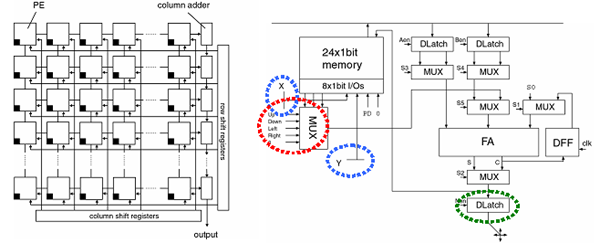

Dynamically Reconfigurable SIMD Architecture

Dynamically Reconfigurable SIMD Architecture

Summary

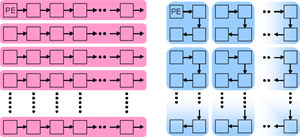

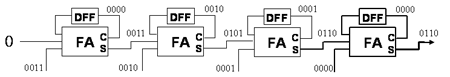

A new SIMD architecture for vision chips has been designed, which features the function of clustering multiple PEs and that enables the hardware to be dynamically reconfigurable. This architecture performs non-local operations efficiently, which conventional SIMD processors are not good at.

Fig.1 Architecture

Fig.2 clustering multiple PEs

Fig.3 operation example of clustered PEs (summation)

Reference

- Takashi Komuro, Shingo Kagami, Masatoshi Ishikawa: A Dynamically Reconfigurable SIMD Processor for a Vision Chip, IEEE Journal of Solid-State Circuits, Vol. 39, No. 1, pp. 265-268 (2004) [PDF]