ホーム >

システム ビジョン デザイン > ビジョンチップ用超並列コンパイラ vcc

ビジョンチップ用超並列コンパイラ vcc

概要

システム ビジョン デザインのプログラミングを容易化するためのコンパイラを開発した。 (1)コード生成効率、(2)モジュールの再利用性、(3)ユーザ利便性の向上を目的に、 以下のような仕組みが導入されている。

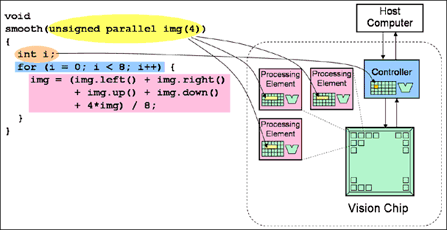

- 通常の C 言語に新しく parallel 型を導入し、ビジョンチップ で行う超並列処理とコントローラで行う逐次処理を同時に記述できるようにした(Fig.1)。

- parallel 型には任意のビット数が指定でき、貴重なメモリ資源を有効利用できるようにした。

- 宣言時にビット長を指定しない不定長 parallel 型変数を導入した。

- parallel 型の条件式を取るパラレル if 文を導入した。

- 隣接画素間の通信などハードウェア固有の機能を組み込み関数という形で提供した。

- 定数畳み込み、複写伝播などのコード最適化をビット単位で行うようにした。

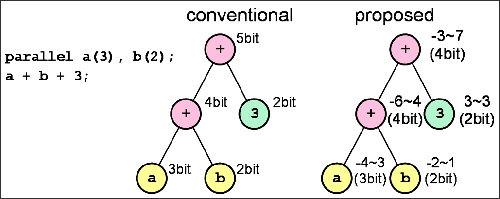

- 変数が取り得る値の最大値と最小値を追跡し、それにより演算結果のビット長を決定する Max-min 法を導入した(Fig.2)。

- 上記のほか、演算子毎にも固有の最適化を行っている。

Fig.1 parallel 型の導入

Fig.2 Max-min 法

参考文献

- 小室孝,鏡慎吾,石川正俊,片山善夫:超並列画像プロセッサのためのビットレベルコンパイラ, 情報処理学会論文誌 コンピューティングシステム, Vol.48, No.SIG13, pp.106-116 (2007)

- Takashi Komuro, Shingo Kagami, Masatoshi Ishikawa, Yoshio Katayama : Development of a Bit-level Compiler for Massively Parallel Vision Chips, IEEE 7th International Workshop on Computer Architecture for Machine Perception(CAMP'05) (Palermo, 2005.7.5)/Proceedings pp.204-209 [PDF]

- 山野高将, 小室孝, 鏡慎吾, 石川正俊:ビジョンチップコンパイラのビットレベル最適化手法, 情報科学技術フォーラム2003 (札幌, 2003.9.10)/一般講演論文集, 第一分冊, pp177-178

- 松内良介, 村田達也, 石井抱, 石川正俊:ビジョンチップシステムのためのソフトウェア開発環境の構築, 情報処理学会計算機アーキテクチャ研究会 (阿蘇, 1997.8.20)/情報処理学会研究報告, Vol.ARC-125, No.7, pp.37-42