|

ビジョンチップシステムの試作 |

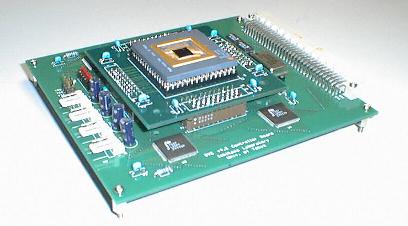

ロボットビジョン等へのビジョンチップの実際の応用に向けて,試作されたビジョ ンチップとコントローラ,インタフェース等をワンボード上に搭載したビジョン チップシステムの試作を行った.試作されたシステムを用いて各種視覚処理アプ リケーションの実行を確認するとともに,実際のロボットビジョンタスク実現の 例として,アクティブビジョンに搭載して高速ターゲットトラッキングを行った.

現在,0.35um プロセスにて試作されたビジョ ンチップを搭載し,ボード上の FPGA(XILINX XC4000)にビジョンチップコントローラ(SPARSIS コア) を実装したシステム全体で,クロック周波数 40MHz での動作を確認してい る.

Fig. 1: 試作されたビジョンチップシステム

[ ホーム | センサフュージョン | ビジュアルサーボ | ビジョンチップ | 光コンピューティング | メンバー | 論文 ]

Ishikawa Namiki laboratory WWW admin: www-admin@k2.t.u-tokyo.ac.jp