|

細粒度な実時間性を保つビジョンチップコントローラアーキテクチャ |

通常の視覚処理を大幅に上回るフレームレートで動作するビジョンチップの制御 には,厳しい実時間性が要求される.さらに,撮像面で入力光の A/D 変換まで もプログラマブルに行えるという汎用ビジョンチップの特長を最大限に活かすた めには,ビジョンチップコントローラには (1) 高いインストラクションレート と (2)インストラクションサイクルの粒度での実時間性の保証が求められる.

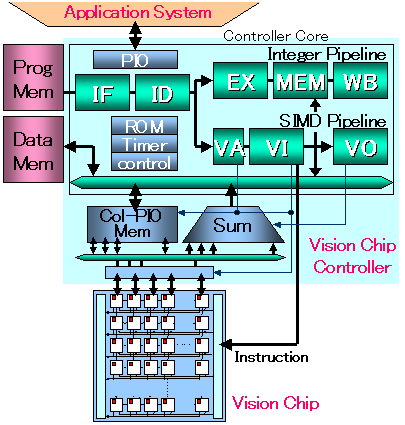

これらの要求を満たすため,新たなビジョンチップコントローラアーキテクチャ SPARSIS の設計を行った.RISC 型 32 ビットマイクロコントローラの パイプラインにビジョンチップの制御フローを統合することでインストラクショ ンレートの向上を図り,かつ,パイプライン内/パイプライン間フォワーディン グ,遅延分岐/ロード,固定レイテンシのメモリアクセスなどによりパイプライ ンのストールを回避し,インストラクションサイクルの粒度での実時間性を保証 している.

Fig. 1: ビジョンチップコントローラアーキテクチャ: SPARSIS

[ ホーム | センサフュージョン | ビジュアルサーボ | ビジョンチップ | 光コンピューティング | メンバー | 論文 ]

Ishikawa Namiki laboratory WWW admin: www-admin@k2.t.u-tokyo.ac.jp