Home >

System Vision Design >

Shared-Memory Multi-SIMD Architecture

Shared-Memory Multi-SIMD Architecture

Summary

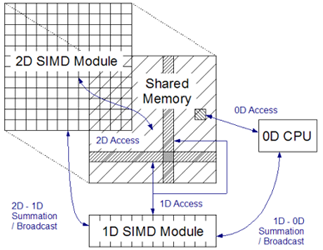

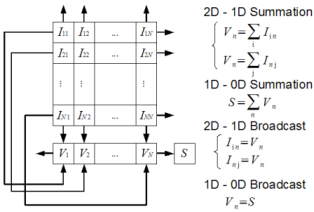

For high speed image recognition in real environment, it is a challenge to accelerate a large amount of computation in image processing, from pre-processing to feature extraction. We designed a vision processor which consists of 2D / 1D parallel SIMD and scaler processing modules that share a memory. The processor has summation and broadcast function between modules, which accelerates required operations in vector processing. Memory sharing reduces cost for data transferring between modules and simplifies implementation of various parallel algorithms.

|

|

| Fig.1 Shared-Memory Multi-SIMD Architecture | Fig.2 Summation / Broadcast Operation |

References

- Kota Yamaguchi, Yoshihiro Watanabe, Takashi Komuro, Masatoshi Ishikawa: Design of a Massively Parallel Vision Processor based on Multi-SIMD Architecture, 2007 IEEE International Symposium on Circuits and Systems (ISCAS2007) (New Orleans, 2007.5.30) / Proceedings, pp.3498-3501. [PDF]

- Kota Yamaguchi, Yoshihiro Watanabe, Takashi Komuro, Masatoshi Ishikawa: Design of a Massively Parallel Vision Processor for High Speed Image Recognition, Proceedings of Forum on Information Technology (FIT2006) (Fukuoka, 2006.09.05), Vol. 1, pp.181-184 (C-012).

- Kota Yamaguchi, Yoshihiro Watanabe, Takashi Komuro, Masatoshi Ishikawa: Design of a High Performance Vision Processor with Shared-Memory Multi-SIMD Architecture, IEICE Technical Committee on Integrated Circuits and Devices (ICD) (Kawasaki, 2006.06.09) / IEICE Technical Report, Vol. 106, No. 92, pp. 89-94 (ICD2006-56).