|

Vision Chip

|

Japanese version

is also available.

Concept

The aim of this project is to realize a high-speed real-time vision

system by integrating photo detectors (PD) and digital processing

elements (PE) on a VLSI chip. This architecture yields remarkably

faster real-time visual processing when compared with conventional

vision systems. We investigate this vision chip architecture from a

whole system integration viewpoint; that is, we are not only

developing full-custom VLSI chips but also algorithms, system

software, and applications such as robotic systems.

Research Contents

System Development

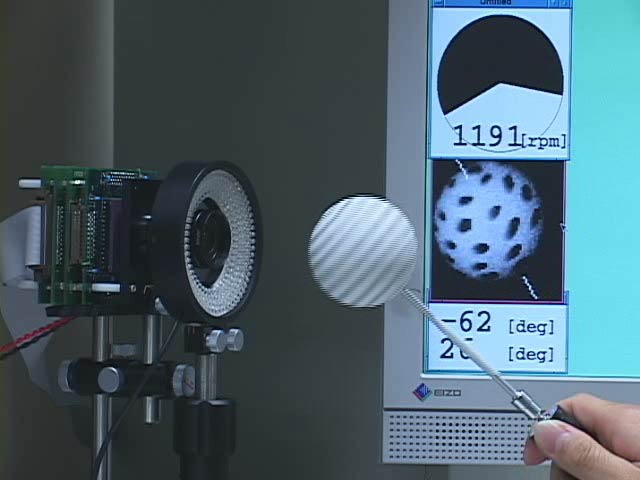

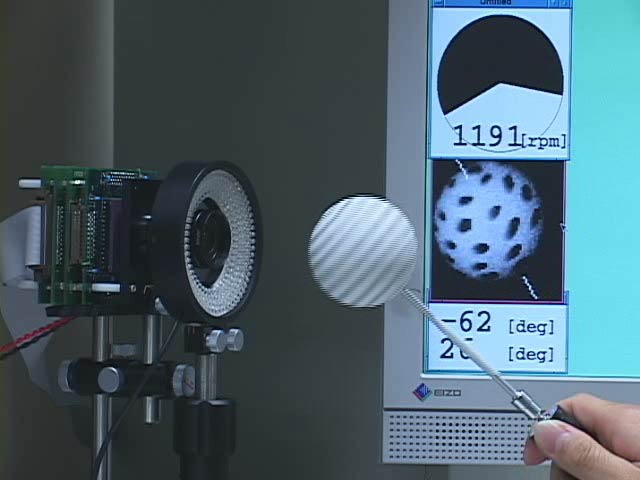

- VCS-IV: Real-time Visual Processing System using Vision Chip

- General-Purpose Digital Vision Chip with 64x64 pixels

- SPARSIS: Vision Chip Controller Architecture

- TVC: High Speed Target Tracking Vision Chip

- CPV: Column Parallel Vision System

Parallel Processing Architectures

-

Dynamically Reconfigurable Vision Chip Architecture

- TVC: High Speed Target Tracking Vision Chip Architecture

- Moment Feature Extraction Architecture

-

S3PE: Massively Parallel Vision Chip Architecture

Photo Detector Technology

Software Environment

- Bit-Level Optimization for Vision Chip Code Generator

- SPE-C: Parallel Programming Language for Vision Chip

Algorithms

Sensor Network

- Sensor Selection Method Considering Communication Delays

Applications

Designs and Implementations in the Past

- VCS-III: Real-Time Visual Processing System using Vision Chip

-

Vision Chip Controller Design

-

1ms Visual Feedback System

-

SPE-4k System

-

2-D Resistive Network with Nonlinear Coordinates

[Home|

Sensor Fusion|

Optoelectronic Computing|

Members|

Papers|

Movies]

Ishikawa Nami Komuro laboratory WWW admin:

www-admin@k2.t.u-tokyo.ac.jp